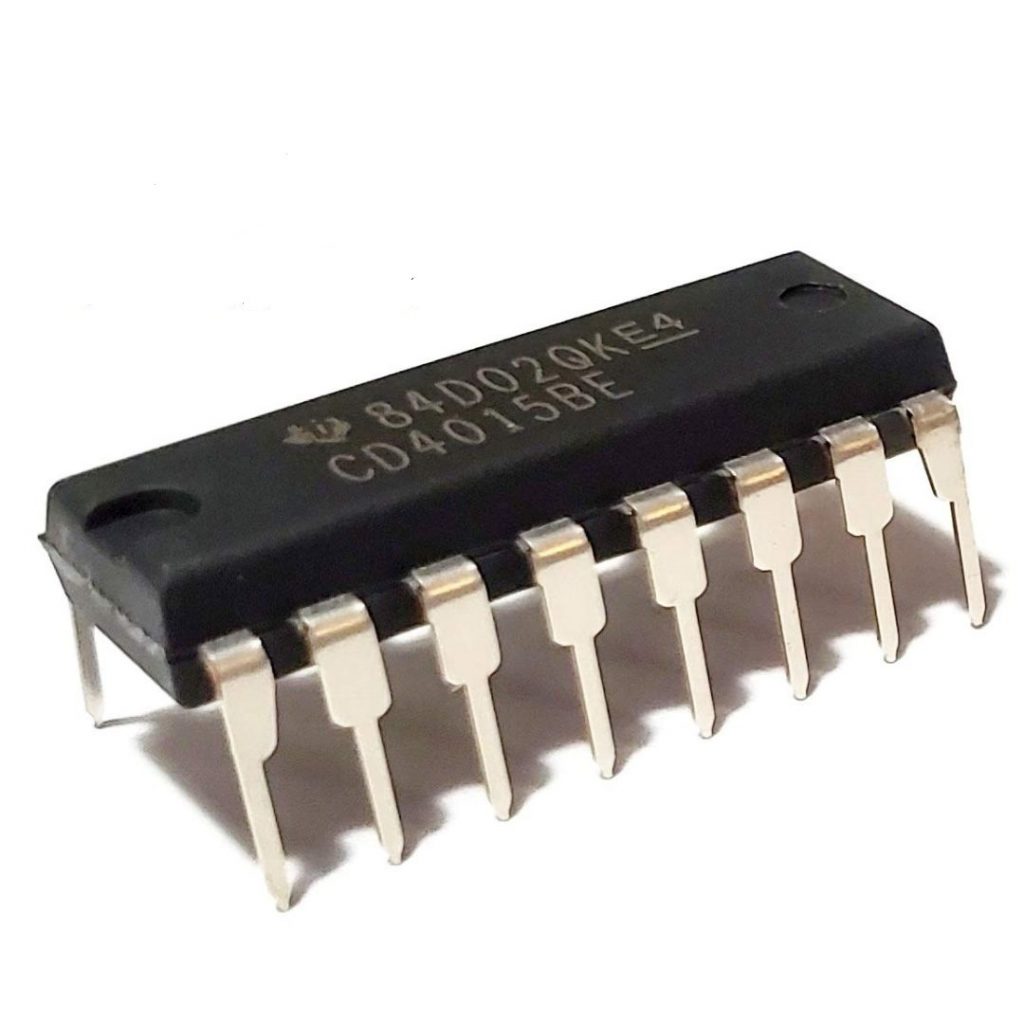

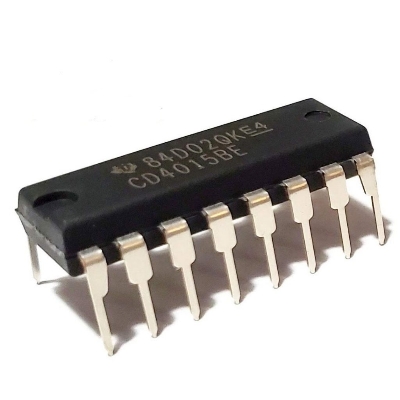

Description: CD4015 IC CD 4015 DIP 16 Pin IC A Class

A Class CD4015BE CD4015 CD-4015 4015 DIP-16 Pin Dual In Package Dual 4 Stage Static Shift Register Serial In Parallel Out IC Breadboard Friendly IC

The CD4015 belongs to the CD4000 IC series. The IC contains two identical, 4-stage, serial input/parallel-output registers with independent “Data”, “Clock,” and “Reset” inputs. The logic level present at the input of each stage is transferred to the output of that stage at each positive-going clock transition. A logic high on the “Reset” input resets all four stages covered by that input. The IC has a wide range of operative conditions and voltages and interfaces directly with CMOS, NMOS, and TTL devices. CD4015 offers various features such as high noise immunity and low thermal dissipation.

What is Static Shift Register?

Static Shift registers are digital memory circuitry found in devices such as calculators, computers, and data processing systems. With a static shift register, data or bits are entered into the system in a serial or parallel manner. data entry is done from one direction, and as more data is added, it shifts positions until the data gets to the output end. The two ends are referred to as the left and right end. Movement of data can be from left to right, from right to left, or in both directions to make a bidirectional register.

CD4015 Key Features

- Wide supply voltage range: 3.0V to 18V

- High noise immunity: 0.45 VDD (typ.)

- Low power TTL: Fan out of 2 driving 74L compatibility: or 1 driving 74LS

- Medium speed operation: 8 MHz (typ.) clock rate

- Fully static design: @VDD − VSS = 10V

CD4015 Pinout

Application

- Serial-input/parallel-output data queuing

- Serial to parallel data conversion

- General-purpose register

- Wide supply voltage range: 3.0V to 18V

- High noise immunity: 0.45 VDD (typ.)

- Low power TTL: Fan out of 2 driving 74L compatibility: or 1 driving 74LS

- Medium speed operation: 8 MHz (typ.) clock rate

- Fully static design: @VDD − VSS = 10V

Login to ask a question

Global Finds

Global Finds  Quick Commerce

Quick Commerce  Electronics & Appliances

Electronics & Appliances  Mother, Baby & Toys

Mother, Baby & Toys  Beauty

Beauty  Sports

Sports  Automotive

Automotive  Stationery, Books & Music

Stationery, Books & Music _20.png) Fashion Luxe

Fashion Luxe _20.jpeg) Home

Home  Garden & Pet Care

Garden & Pet Care  Special Weekly Offer

Special Weekly Offer  Grocery

Grocery  Global Finds

Global Finds  Quick Commerce

Quick Commerce  Electronics & Appliances

Electronics & Appliances  Mother, Baby & Toys

Mother, Baby & Toys  Beauty

Beauty  Sports

Sports  Automotive

Automotive  Stationery, Books & Music

Stationery, Books & Music _20.png) Fashion Luxe

Fashion Luxe _20.jpeg) Home

Home  Garden & Pet Care

Garden & Pet Care  Special Weekly Offer

Special Weekly Offer  Grocery

Grocery